آیا می دانید چگونه مشکل EMI را هنگام طراحی PCB چند لایه حل کنید؟

اجازه بدهید به شما بگویم!

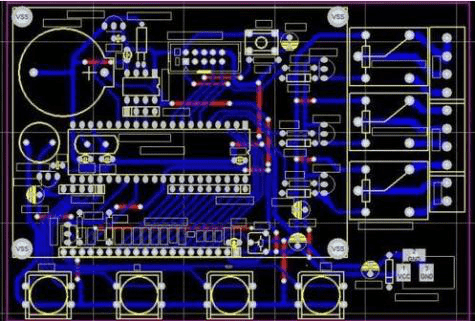

راه های زیادی برای حل مشکلات EMI وجود دارد.روش های مدرن سرکوب EMI عبارتند از: استفاده از پوشش سرکوب کننده EMI، انتخاب قطعات سرکوب کننده EMI مناسب و طراحی شبیه سازی EMI.بر اساس اساسی ترین طرح PCB، این مقاله عملکرد پشته PCB را در کنترل تابش EMI و مهارت های طراحی PCB مورد بحث قرار می دهد.

اتوبوس برق

جهش ولتاژ خروجی آی سی را می توان با قرار دادن ظرفیت خازنی مناسب در نزدیکی پایه پاور آی سی تسریع کرد.با این حال، این پایان مشکل نیست.به دلیل پاسخ فرکانسی محدود خازن، خازن نمی تواند توان هارمونیک مورد نیاز برای هدایت خروجی آی سی را در باند فرکانس کامل تولید کند.علاوه بر این، ولتاژ گذرا تشکیل شده در گذرگاه قدرت باعث افت ولتاژ در هر دو انتهای اندوکتانس مسیر جداسازی خواهد شد.این ولتاژهای گذرا منابع اصلی تداخل EMI حالت رایج هستند.چگونه می توانیم این مشکلات را حل کنیم؟

در مورد آی سی روی برد مدار ما، لایه قدرت اطراف آی سی را می توان به عنوان یک خازن با فرکانس بالا خوب در نظر گرفت که می تواند انرژی نشت شده توسط خازن گسسته را جمع آوری کند که انرژی فرکانس بالا را برای خروجی تمیز فراهم می کند.علاوه بر این، اندوکتانس یک لایه قدرت خوب کوچک است، بنابراین سیگنال گذرا سنتز شده توسط سلف نیز کوچک است، بنابراین EMI حالت رایج کاهش مییابد.

البته اتصال بین لایه منبع تغذیه و پایه منبع تغذیه آی سی باید تا حد امکان کوتاه باشد، زیرا لبه بالارونده سیگنال دیجیتال سریعتر و سریعتر است.بهتر است مستقیماً آن را به پدی که پایه IC پاور قرار دارد وصل کنید که نیاز به بحث جداگانه دارد.

برای کنترل EMI حالت مشترک، لایه قدرت باید یک جفت لایه قدرت به خوبی طراحی شده باشد تا به جدا شدن کمک کند و اندوکتانس به اندازه کافی پایین داشته باشد.ممکن است برخی از مردم بپرسند که چقدر خوب است؟پاسخ به لایه قدرت، مواد بین لایه ها و فرکانس کاری (یعنی تابعی از زمان افزایش آی سی) بستگی دارد.به طور کلی، فاصله لایه های قدرت 6 میل است و لایه میانی از مواد FR4 است، بنابراین ظرفیت معادل در هر اینچ مربع از لایه قدرت حدود 75 pF است.بدیهی است که هرچه فاصله لایه ها کوچکتر باشد، ظرفیت خازنی بیشتر است.

دستگاه های زیادی با زمان افزایش 100-300ps وجود ندارد، اما با توجه به نرخ توسعه فعلی آی سی، دستگاه هایی با زمان افزایش در محدوده 100-300ps نسبت بالایی را اشغال خواهند کرد.برای مدارهایی با زمان افزایش 100 تا 300 PS، فاصله لایه 3 میلیمتری دیگر برای اکثر برنامهها قابل استفاده نیست.در آن زمان، لازم است فناوری لایهلایهسازی را با فاصله بین لایهای کمتر از 1 میلیمیل اتخاذ کرد و مواد دی الکتریک FR4 را با موادی با ثابت دی الکتریک بالا جایگزین کرد.اکنون، سرامیک ها و پلاستیک های گلدانی می توانند الزامات طراحی مدارهای زمان خیز 100 تا 300ps را برآورده کنند.

اگرچه ممکن است در آینده از مواد و روشهای جدیدی استفاده شود، مدارهای زمانی خیزش معمولی 1 تا 3 ns، فاصله لایهها 3 تا 6 میل و مواد دیالکتریک FR4 معمولاً برای کنترل هارمونیکهای سطح بالا و ایجاد سیگنالهای گذرا به اندازه کافی کافی هستند. ، EMI حالت رایج را می توان بسیار کم کاهش داد.در این مقاله، نمونه طراحی انباشته لایه مدار مدار چاپی ارائه شده است و فاصله لایه ها 3 تا 6 میل در نظر گرفته شده است.

محافظ الکترومغناطیسی

از نقطه نظر مسیریابی سیگنال، یک استراتژی لایه بندی خوب باید این باشد که همه ردیابی های سیگنال را در یک یا چند لایه قرار دهیم که در کنار لایه قدرت یا صفحه زمین هستند.برای منبع تغذیه، یک استراتژی لایه بندی خوب باید این باشد که لایه قدرت در مجاورت صفحه زمین باشد و فاصله بین لایه قدرت و صفحه زمین باید تا حد امکان کوچک باشد، که ما به آن استراتژی "لایه بندی" می گوییم.

پشته PCB

چه نوع استراتژی انباشتگی می تواند به محافظت و سرکوب EMI کمک کند؟طرح انباشته لایه ای زیر فرض می کند که جریان منبع تغذیه روی یک لایه جریان می یابد و ولتاژهای تک یا چند ولتاژ در قسمت های مختلف همان لایه توزیع می شود.مورد چند لایه قدرت بعدا مورد بحث قرار خواهد گرفت.

صفحه 4 لایه

مشکلات احتمالی در طراحی لمینت های 4 لایه وجود دارد.اول از همه، حتی اگر لایه سیگنال در لایه بیرونی و صفحه قدرت و زمین در لایه داخلی باشد، فاصله بین لایه قدرت و صفحه زمین هنوز خیلی زیاد است.

اگر هزینه مورد نیاز اول باشد، دو گزینه زیر برای تخته 4 لایه سنتی را می توان در نظر گرفت.هر دوی آنها می توانند عملکرد سرکوب EMI را بهبود بخشند، اما فقط برای مواردی مناسب هستند که چگالی قطعات روی برد به اندازه کافی کم باشد و ناحیه کافی در اطراف قطعات وجود داشته باشد (برای قرار دادن پوشش مسی مورد نیاز برای منبع تغذیه).

اولین طرح ترجیحی است.لایه های بیرونی PCB همه لایه هستند و دو لایه میانی لایه سیگنال / قدرت هستند.منبع تغذیه در لایه سیگنال با خطوط گسترده هدایت می شود که باعث می شود امپدانس مسیر جریان منبع تغذیه کم و امپدانس مسیر میکرو نوار سیگنال پایین باشد.از دیدگاه کنترل EMI، این بهترین ساختار PCB 4 لایه موجود است.در طرح دوم، لایه بیرونی برق و زمین را حمل می کند و دو لایه میانی حامل سیگنال است.در مقایسه با برد 4 لایه سنتی، بهبود این طرح کمتر است و امپدانس بین لایه ای به خوبی برد 4 لایه سنتی نیست.

اگر قرار است امپدانس سیمکشی کنترل شود، طرح انباشتگی بالا باید بسیار مراقب باشد تا سیمکشی را زیر جزیره مسی منبع تغذیه و زمین قرار دهد.علاوه بر این، جزیره مسی در منبع تغذیه یا لایه باید تا حد امکان به هم متصل شود تا از اتصال بین DC و فرکانس پایین اطمینان حاصل شود.

صفحه 6 لایه

اگر تراکم قطعات روی برد 4 لایه زیاد باشد صفحه 6 لایه بهتر است.با این حال، اثر محافظ برخی از طرح های انباشته در طراحی تخته 6 لایه به اندازه کافی خوب نیست و سیگنال گذرا گذرگاه قدرت کاهش نمی یابد.دو نمونه در زیر مورد بحث قرار گرفته است.

در حالت اول منبع تغذیه و زمین به ترتیب در لایه دوم و پنجم قرار می گیرند.به دلیل امپدانس بالای منبع تغذیه با روکش مسی، کنترل تابش EMI حالت رایج بسیار نامطلوب است.اما از نظر کنترل امپدانس سیگنال، این روش بسیار صحیح است.

در مثال دوم منبع تغذیه و زمین به ترتیب در لایه سوم و چهارم قرار می گیرند.این طرح مشکل امپدانس روکش مسی منبع تغذیه را حل می کند.به دلیل عملکرد ضعیف محافظ الکترومغناطیسی لایه 1 و لایه 6، EMI حالت دیفرانسیل افزایش می یابد.اگر تعداد خطوط سیگنال در دو لایه خارجی کمترین باشد و طول خطوط بسیار کوتاه باشد (کمتر از 1/20 از بالاترین طول موج هارمونیک سیگنال)، طرح می تواند مشکل حالت دیفرانسیل EMI را حل کند.نتایج نشان میدهد که سرکوب EMI حالت دیفرانسیل زمانی خوب است که لایه بیرونی با مس پر شود و ناحیه روکش مسی زمین (هر بازه طول موج 1/20) باشد.همانطور که در بالا ذکر شد، مس باید گذاشته شود

زمان ارسال: ژوئیه-29-2020